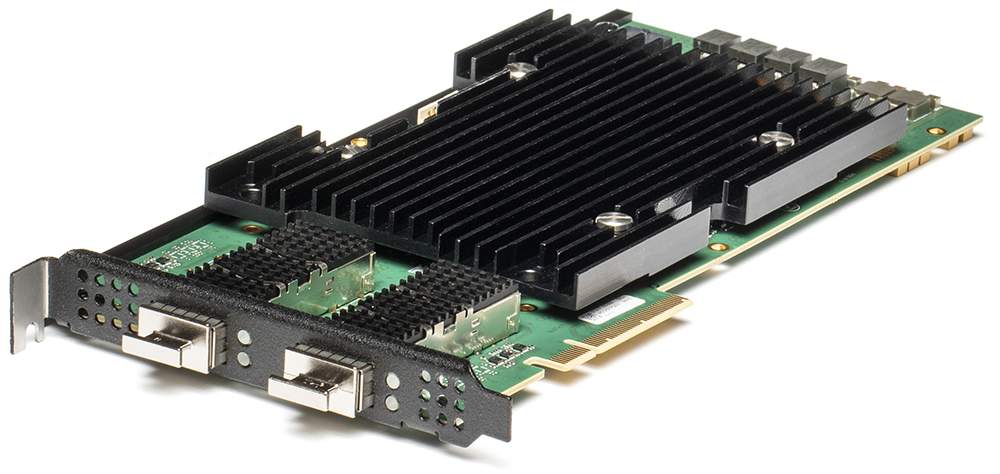

Xena Loki-100G-5S-2P

Xena Loki-100G-5S-2P

1モジュールで100G Ethernet に2ポート対応。100G/ 50G/ 40G/ 25G/ 10G bps 対応 Ethernet テストモジュール

Xena Loki-100G-5S-2P は、5つの Ethernet メディアレート (100G, 50G, 40G, 25G, 10G bps) に対応した ValkyrieBay/ ValkyrieCompact 用テストモジュールです。

本モジュールは切り替え式で用いる QSFP28/ QSFP+ メディアI/Fを2つ実装し、

- QSFP28: 2x 100GbE, 4x 50GbE, 8x 25GbE

- QSFP+: 2x 40GbE, 8x 10GbE

のジェネレート構成が可能です。(要別途メディアモジュール)

特徴

- デュアルポート100Gモジュール、ポート単価で抜群のコストパフォーマンスを実現

- 2種のメディアI/Fに対応 (QSFP28/ QSFP+)

- 5種類の Ethernet メディアレートに対応(2x 100Gbps, 4x 50Gbps, 2x 40Gbps , 8x 25Gbps, 8x 10Gbps)

- ハイコストパフォーマンス

- アイダイアグラム機能

- 3年間のハードウェア保証・ソフトウェアアップデートサービスを提供

ユニークなアイダイアグラム機能

Xena Loki-100G-5S-2P は、アイダイアグラムと呼ばれるユニークな信号品質解析機能を包含しています。

これはQSFP28/ QSFP+ ポートを使用する際にValkyrieManager ソフトウェアの “Resource Properties” タブに現れる追加パネル、 “Advanced PHY Features” で確認することができます。

このパネルでは、4x 10Gまたは4x 25Gリンクに関連した4つの受信SerDesに対する制御及びモニタを物理レベルで行います。またビットエラーレート (BER)アイダイアグラムの作成や、水平BERカーブからリンクBERの評価、及び送受信方向のPHYチューニングの管理も可能です。

仕組み

BERアイダイアグラムは、RXを平衡化した後、信号品質の直接的なビジュアル化を提供します。アイダイアグラムは、PHYのステップバイステップにより得られたサンプリングポイントから時間軸(標本化遅延)と振幅軸(0/1閾値設定による)を変化させる事で生成されます。

各サンプリングポイント (X, Y) では100万ビットが測定され、ビットエラーの数がカウントされ簡単な境界がBERに与えられます。

ダイヤグラムの見方

カラーマップは、各ポイントに於ける、測定された100万(最高赤)から0(黒)のビットエラーレートを示します。色のスケールはログ分布を取ります。より高い分解能はより鮮明なダイアグラムを与え、X, Yのより高い値は水平、垂直バスタブカーブの評価により高い精度を、各々に与えます。

アイデータテーブルは、幅や高さ、ジッターなどアイパターンが持つ幾つかのパラメーターの評価手法を提供します。

| ポート仕様 | |

|---|---|

| 対応メディアレート |

QSFP28: 100Gbps, 50Gbps, 25Gbps QSFP+: 40Gbps, 10Gbps |

| テストポート数 | 2x 100GbE/ 4x 50GbE/ 2x 40GbE/ 8x 25GbE/ 8x 10GbE |

| 対応インタフェース |

同一のインタフェース設定の際に双方のケージの同時稼働が可能。 |

| Forward Error Correction (FEC) |

RS-FEC (Reed Solomon) 528,514,t=7, IEEE 802.3 Clause 91 (100GE) RS-FEC (Reed Solomon) 544,514,t=15, IEEE 802.3 Clause 134 (50GE PAM4) RS-FEC (Reed Solomon) 528,514,t=7, IEEE 802.3 Clause 108 (25GE) RS-FEC (Reed Solomon) 528,514,t=7, 25/50G Ethernet Consortium (25/50GE) 準拠 |

| トランシーバ数 |

2x QSFP28/ QSFP+ メディアI/F |

| ポート統計機能 | リングステート、FCSエラー、ポーズフレーム、ARP/PING、エラー挿入、トレーニングパケット |

| フレーム間隔(IFG) | 16~56byte(デフォルト20byte: 8Bプリアンブル(SFDを含む)+12B IFG) |

| 送信ラインレート | アイドルギャップを強制する事で実効ラインレートを-1,000ppm(-10ppm単位)まで調整可能 |

| 送信ラインクロック | -400~400ppm(0.001ppmステップ)の範囲で調整可能(全ポート共有) |

| ARP/PING | ポート毎にIP, MACアドレスを設定可能 |

| フィールドアップグレード | FPGAファームウエア、操作用ソフトウエア共に完全対応 |

| ヒストグラム統計 | ポート毎の2つのリアルタイムヒストグラム。各ヒストグラムはRX/TXパケット長、全トラフィック、または特定のトラフィックに対する遅延分布。フィルター機能を提供 |

| TX無効機能 | TXポートのリンクを無効にする事が可能 |

| IGMPv2マルチキャスト機能 | IGMPv2を用いたマルチキャストへの連続的な参加が可能。期間を変更できるインターバル設定付き |

| ループバックモード |

|

| 発振器特性 |

|

| 送信エンジン | |

| ポート毎のストリーム数 | 256個(ワイヤスピード) |

| ストリーム毎のテストペイロード挿入 | ワイヤスピードにて、タイムスタンプ、シーケンス番号、各ヘッダーでのFCSを包含したパケットを送出可能。 |

| ストリーム統計 | TX Mbit/s、packets/s、パケット数、バイト数、FCS エラー、ポーズフレーム |

| 帯域幅プロファイル | バーストサイズ及び密度を定義。ユニフォームとバースト的な帯域幅プロファイルストリームは交互に配置が可能 |

| フィールド変更機能 | 値の増加、減少、ランダム化が可能な16bitフィールド変更機能。各フィールド変更機能は、設定可能なビットマスク、繰り返し、最小、最大、ステップパラメータを包含。 ストリーム毎に8個のフィールド変換機能を使用可能。 |

| パケット長制御 | パケット長の固定、ランダム、バタフライ、増長が可能。 パケット長は56byte~12288byteまで対応。 |

| パケットペイロード | ユーザ定義の1~18byteパターン、8bitインクリメントパターンの繰り返し使用が可能 |

| エラー生成 | 最小56byte最大9200byteのパケット長、シーケンス挿入、順番違い、ペイロード完全性、FCSエラーを生成可能 |

| TXパケットヘッダー及びRXデコード機能 | Ethernet、Ethernet II、VLAN、ARP、IPv4、IPv6、UDP、TCP、LLC、SNAP、GTP、ICMP、RTP、RTCP、STP、MPLS、PBB、及びユーザー定義 |

| パケットスケジュールモード |

|

| 受信エンジン | |

| ポート毎にトレース可能なストリーム数 | 2016(ワイヤースピード) |

| 受信パケットのテストペイロード自動検知機能 | レイテンシ、ロス、ペイロード完全性、シーケンスエラー、順番違いのチェックや分析のリアルタイムな報告 |

| ジッター計測 | MEF10に準拠したジッター(パケット遅延変動)計測。8nsの確度で32ストリームまで計測可能 |

| ストリーム統計 |

|

| 遅延計測確度 | ±32 ns |

| 遅延計測分解能 | 8 ns(遅延計測は校正可能であり、トランシーバモジュールからの遅延を除去可能) |

| フィルター数 |

|

| フィルター統計 | フィルタ毎:RX Mbit/s、パケット/s、パケット数、バイト数 |

| キャプチャ | |

| キャプチャ機能 | テストペイロードを除く全トラフィック、FCSエラー、フィルタマッチ |

| キャプチャ スタート・ストップトリガ | 無し、FCSエラー、フィルタマッチ |

| キャプチャ可能な パケットサイズ | 16~12288bytes |

| ポート毎の キャプチャバッファサイズ |

256KB: 100Gbps I/F 128KB: 40Gbps I/F |

| 低速キャプチャバッファ | 4096パケット |

| その他のPHY機能 | |

| 送信平衡制御 |

|